華為芯片堆疊封裝專利公開

奈圖爾科技(www.ntooler.com)整理消息:

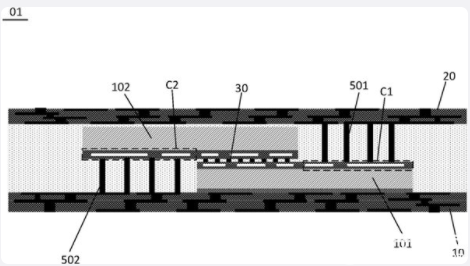

近日,國家知識(shí)產(chǎn)權(quán)局官網(wǎng)公開的信息顯示,華為技術(shù)有限公司公開了“一種芯片堆疊封裝及終端設(shè)備”專利。

據(jù)摘要顯示,本公開涉及半導(dǎo)體技術(shù)領(lǐng)域,其能夠在保證供電需求的同時(shí),解決因采用硅通孔技術(shù)而導(dǎo)致的成本高的問題。

(截圖自國家專利局)

(截圖自國家專利局)

專利文件顯示,該芯片堆疊封裝包括:

設(shè)置于首根走線結(jié)構(gòu) (10) 和第二走線結(jié)構(gòu) (20) 之間的首根芯片 (101) 和第二芯片 (102);

所述首根芯片 (101) 的有源面 (S1) 面向所述第二芯片 (102) 的有源面 (S2);

首根芯片 (101) 的有源面 (S1) 包括首根交疊區(qū)域 (A1) 和首根非交疊區(qū)域 (C1),第二芯片 (102) 的有源面 (S2) 包括第二交疊區(qū)域 (A2) 和第二非交疊區(qū)域 (C2);

首根交疊區(qū)域 (A1) 與第二交疊區(qū)域 (A2) 交疊,首根交疊區(qū)域 (A1) 和第二交疊區(qū)域 (A2) 連接;

首根非交疊區(qū)域 (C1) 與第二走線結(jié)構(gòu) (20) 連接;

第二非交疊區(qū)域 (C2) 與首根走線結(jié)構(gòu) (10) 連接。

所謂的芯片堆疊技術(shù)究竟是什么?

“芯片堆疊”技術(shù)近段時(shí)間經(jīng)常聽到,在前段時(shí)間蘋果舉行線上發(fā)布會(huì)時(shí),推出了號(hào)稱“史上最強(qiáng)”的Apple M1 ultra,這就是一種采用堆疊思路設(shè)計(jì)的芯片。

M1 ultra將兩枚M1 Max中隱藏的芯片間互連模塊(die-to-die connector)通過技術(shù)手段整合在一起,蘋果將其稱之為“Ultra Fusion”架構(gòu),擁有1萬多個(gè)信號(hào)點(diǎn),互連帶寬高達(dá)2.5TB/s,而且延遲、功耗都非常低。

通過這種方式組合而成的M1 Ultra,規(guī)格基本上是M1 Max的翻倍。同樣是采用了5nm制造工藝,但M1 Ultra的晶體管數(shù)量卻高達(dá)1140億個(gè),統(tǒng)一內(nèi)存高達(dá)到128GB,總帶寬800GB/s。

那么所謂的芯片堆疊技術(shù)究竟是什么?據(jù)了解,堆疊技術(shù)也可以叫做3D堆疊技術(shù),是利用堆疊技術(shù)或通過互連和其他微加工技術(shù)在芯片或結(jié)構(gòu)的Z軸方向上形成三維集成,信號(hào)連接以及晶圓級(jí),芯片級(jí)和硅蓋封裝具有不同的功能。針對(duì)包裝和可靠性技術(shù)的三維堆疊處理技術(shù)。

該技術(shù)用于微系統(tǒng)集成,是在片上系統(tǒng)(SOC)和多芯片模塊(MCM)之后開發(fā)的先進(jìn)的系統(tǒng)級(jí)封裝制造技術(shù)。 在傳統(tǒng)的SiP封裝系統(tǒng)中,任何芯片堆棧都可以稱為3D,因?yàn)樵赯軸上功能和信號(hào)都有擴(kuò)展,無論堆棧位于IC內(nèi)部還是外部。

目前,3D芯片技術(shù)的類別包括:基于芯片堆疊的3D技術(shù),基于有源TSV的3D技術(shù),基于無源TSV的3D技術(shù),以及基于芯片制造的3D技術(shù)。

筆者注意到,去年華為就曾被曝出“雙芯疊加”專利,這種方式可以讓14nm芯片經(jīng)過優(yōu)化后比肩7nm性能。但當(dāng)時(shí)曝光的這種通過堆疊的方式與蘋果的“Ultra Fusion”架構(gòu)還是有所不同。也許有很多人理解雙芯片堆疊是指將兩顆獨(dú)立芯片進(jìn)行物理堆疊的方式去實(shí)現(xiàn)性能突破,其實(shí)這是非常嚴(yán)重的錯(cuò)誤,如果單單依靠物理堆疊,那么會(huì)有非常多的弊端無法解決,例如兼容性,穩(wěn)定性,發(fā)熱控制這些都是沒法通過物理堆疊來解決問題的,在設(shè)計(jì)思路上面就會(huì)走上歧路,得不償失也毫無意義。

雙芯疊加層級(jí)運(yùn)用于設(shè)計(jì)和生產(chǎn)初期,也就是說在設(shè)計(jì)過程中將原來的一顆芯片設(shè)計(jì)成雙層芯片然后利用自己獨(dú)特的技術(shù),來將這兩層芯片封裝在一顆芯片中,通過同步信號(hào)方式與一些其他方法就可以激活雙層芯片共同發(fā)力,從而實(shí)現(xiàn)芯片性能突破。所以說一個(gè)物理層堆疊,一個(gè)設(shè)計(jì)之初就開始改變?cè)O(shè)計(jì)思路,這是完全不同的兩個(gè)方式。

因此雖然同樣是指雙芯片組合成單個(gè)主芯片,但蘋果與華為可以說是兩種截然不同的方式。無論如何,雙芯片組合帶來的結(jié)果必然是1+1>1,但不等于2。

當(dāng)然,無論是華為的雙芯疊加技術(shù)還是蘋果的Ultra Fusion架構(gòu),在當(dāng)前芯片工藝水平發(fā)展接近極限的情況下,“雙芯堆疊”設(shè)計(jì)的方式不失為一種好的選擇。理論上來說,兩顆芯片可以將任務(wù)分工處理,形成更強(qiáng)的運(yùn)行效率,而其中重點(diǎn)所需要解決的,無非就是功耗、信號(hào)同步、數(shù)據(jù)流協(xié)同處理等方面的問題。

在前不久舉辦的華為2021年業(yè)績發(fā)布會(huì)上,華為輪值董事長郭平表態(tài)稱,未來華為可能會(huì)采用多核結(jié)構(gòu)的芯片設(shè)計(jì)方案,以提升性能。同時(shí),采用面積換性能,用堆疊換性能,使得不那么先進(jìn)的工藝也能持續(xù)讓華為在未來的產(chǎn)品里面,能夠具有競(jìng)爭力。

在去年12月,華為公司還投資6億元成立了一家電子制造的全資子——華為精密制造有限公司,經(jīng)營范圍為光通信設(shè)備制造,光電子器件制造,電子元器件制造和半導(dǎo)體分立器件制造。當(dāng)時(shí)就有內(nèi)部人士稱,該公司具備一定規(guī)模的量產(chǎn)和小批量試制(能力),但主要用于滿足自有產(chǎn)品的系統(tǒng)集成需求。“不生產(chǎn)芯片,主要是部分核心器件、模組、部件的精密制造。”同時(shí),經(jīng)營范圍中提及的“半導(dǎo)體分立器件“主要是分立器件的封裝、測(cè)試。如此來看,華為對(duì)于芯片堆疊路線早有清晰的規(guī)劃,沒準(zhǔn)已經(jīng)投入制造環(huán)節(jié)。

此外,從華為將海思列為了一級(jí)部門的重大業(yè)務(wù)架構(gòu)調(diào)整來看,這預(yù)示著其戰(zhàn)略重心的重新配置。在過去相當(dāng)長的一段時(shí)間里,海思只是華為2012實(shí)驗(yàn)室下面的一個(gè)部門,在高端的產(chǎn)品也都是自用。現(xiàn)在,華為將海思列為一級(jí)業(yè)務(wù)部門,在很大程度上預(yù)示著,未來華為的芯片產(chǎn)品,將從“部分商用”調(diào)整為“全面商用”,華為也將繼續(xù)加大在芯片領(lǐng)域的人才投入和技術(shù)投入。

掃一掃,關(guān)注我們

相關(guān)新聞

- CFCF2023基調(diào)論壇:大模型、全光網(wǎng)加速400G/800G切換時(shí)間點(diǎn)

- 光纖通信在電力系統(tǒng)繼電保護(hù)設(shè)備的應(yīng)用

- 移動(dòng)全千兆網(wǎng)絡(luò)惠及千余小區(qū)群眾

- 華為投資兩家毫米波及測(cè)試測(cè)量相關(guān)國內(nèi)企業(yè)

- 低功耗無線模塊超遠(yuǎn)距離無線傳輸實(shí)現(xiàn)中繼的方法

- Dell'Oro:2020年全球光傳輸設(shè)備市場(chǎng)收入僅增長1%

- 我國建成全球規(guī)模較大的光纖網(wǎng)絡(luò)和4G網(wǎng)絡(luò)

- Kiran Mukkavilli:專注于解決4G和5G的基本波形問題

- 澳大利亞團(tuán)隊(duì)實(shí)現(xiàn)超高帶寬網(wǎng)速達(dá)44.2Tbps

- 全球IPv6測(cè)試中心廣州實(shí)驗(yàn)室揭牌